计算机网络 第五章 接口层原理与协议

Kapitel 5 接口层原理与协议 5.1 接口层基础 TCP/IP体系结构 物理网络连接方式(拓扑结构):节点到节点连接、共享式连接、交换式连接 接口层功能 物理层:提供位流服务 数据链路层:提供可靠或不可靠的传输服务 接口层技术分类 有多种接口层技术,传统上大致可以分成三类:局域网、城域网、广域网 5.2 局域网体系结构与组网方法 局域网体系结构与数据封装 介质访问控制层(Medium Access Control ) 物理节点寻址 差错控制 介质访问控制(共享式连接) 逻辑链路控制层(Logical Link Control) 链路层的复用和分用 可靠数据传输 5.3 局域网编址与ARP协议 MAC地址—物理地址 32位IP地址: 网络层地址(逻辑地址):标识主机或路由器的一个接口 主要用于IP数据包的路由转发 48位MAC地址(物理地址): 物理地址:在相同的物理网络中,标识一个节点 对于大多数局域网,采用48位MAC地址 位于网卡的ROM或EPROM中 扁平地址,无层次,需要唯一 ARP协议 A已知B的IP地址,需要获 ...

汇编语言与逆向技术基础 八、静态逆向技术

汇编语言与逆向技术基础 八、静态逆向技术 知识点 逆向技术 IDA Pro 简介 IDA Pro 窗口 IDA Pro 的操作 交叉引用 函数分析 图形化显示 增强反汇编的相关功能 逆向技术 逆向工程 逆向工程(又称 逆向技术 ),是一种产品设计技术再现过程 对一项目标产品进行逆向分析及研究,从而演绎并得出该产品的处理流程、组织结构、功能特性及技术规格等设计要素,以制作出功能相近,但又不完全一样的产品。 逆向工程源于商业及军事领域中的硬件分析 其主要目的是在不能轻易获得必要的生产信息的情况下,直接从成品分析,推导出产品的设计原理 软件逆向工程 软件逆向工程(Software Reverse Engineering)是指根据软件程序的反汇编代码(静态)和执行过程(动态),通过逆向分析来推导出软件具体的实现方法。 软件逆向工程可能会被误认为是对知识产权的严重侵害,但是在实际应用上,反而可能会保护知识产权所有者。 漏洞发掘 取证 性能分析 软件保护 逆向分析技术 静态分析 IDA Pro 动态分析 OllyDbg WinDbg IDA Pro 简介 IDA Pr ...

CA9 数据级并行性 (1)

CA9 数据级并行性 (1) 引言 SIMD 体系结构利用了数据并行性 面向矩阵的科学计算 面向多媒体的图像和声音处理 机器学习算法 SIMD比MIMD更节能 与MIMD相比,SIMD单挑指令可以同时对许多数据进行操作 个人移动设备使SIMD更具吸引力 在SIMD架构中,程序员从代码顺序执行的角度来思考问题,获得代码并行执行的加速比。 SIMD 并行性 SIMD 的三种变形 矢量体系结构 SIMD 扩展指令集 图形处理单元GPUs Intel x86 预计每年每个芯片处理器增加两个处理核 SIMD 宽度每四年翻一倍 SIMD 的潜在加速比是 MIMD 的两倍 矢量体系结构 将许多数据操作扩展为流水执行 对微处理器来说,代价昂贵 需要更多的晶体管资源 需要最够的DRAM带宽 SIMD 扩展指令集 1996年,MMX multimedia extensions SSE streaming SIMD extensions AVX advanced vector extensions 图形处理单元 与矢量体系结构共享特征,但具有自己的特性 独特的生态环境: ...

网络技术与应用 第七章 IP 地址与 ARP

IP 地址的作用 为什么需要 IP 地址? 屏蔽各种物理网络的地址差异 每种物理网络都有各自的技术特点,其物理地址也各不相同 统一物理地址的表示方法不现实 互联网对各种物理网络地址的“统一”通过IP地址在IP层完成 IP 地址的作用 指定计算机到互联网的一个连接 与互联网有多个物理连接的主机有多个 IP 地址 多个 IP 地址可绑定到一条物理连接上 多宿主主机——多块网卡的计算机 IP 地址的组成 IP 地址的层次结构 IP 地址的组成 IP地址的长度为32位二进制数 网络号netid:标识互联网中一个特定网络 主机号hostid:标示网络中主机的一个特定连接 IP 编制的特点 优点:IP编址方式携带了位置信息 给出IP地址就能知道它位于哪个网络 路由简单 缺点:主机在网络间移动,IP地址须跟随变化 IP 地址的分类 书上144页 特殊的 IP 地址形式 网络地址 构成:一个有效的网络号和一个全“0”的主机号 例:IP地址为202.93.120.44的主机所处的网络为202.93.120.0,主机号为44 广播地址 直接广播:主机向 ...

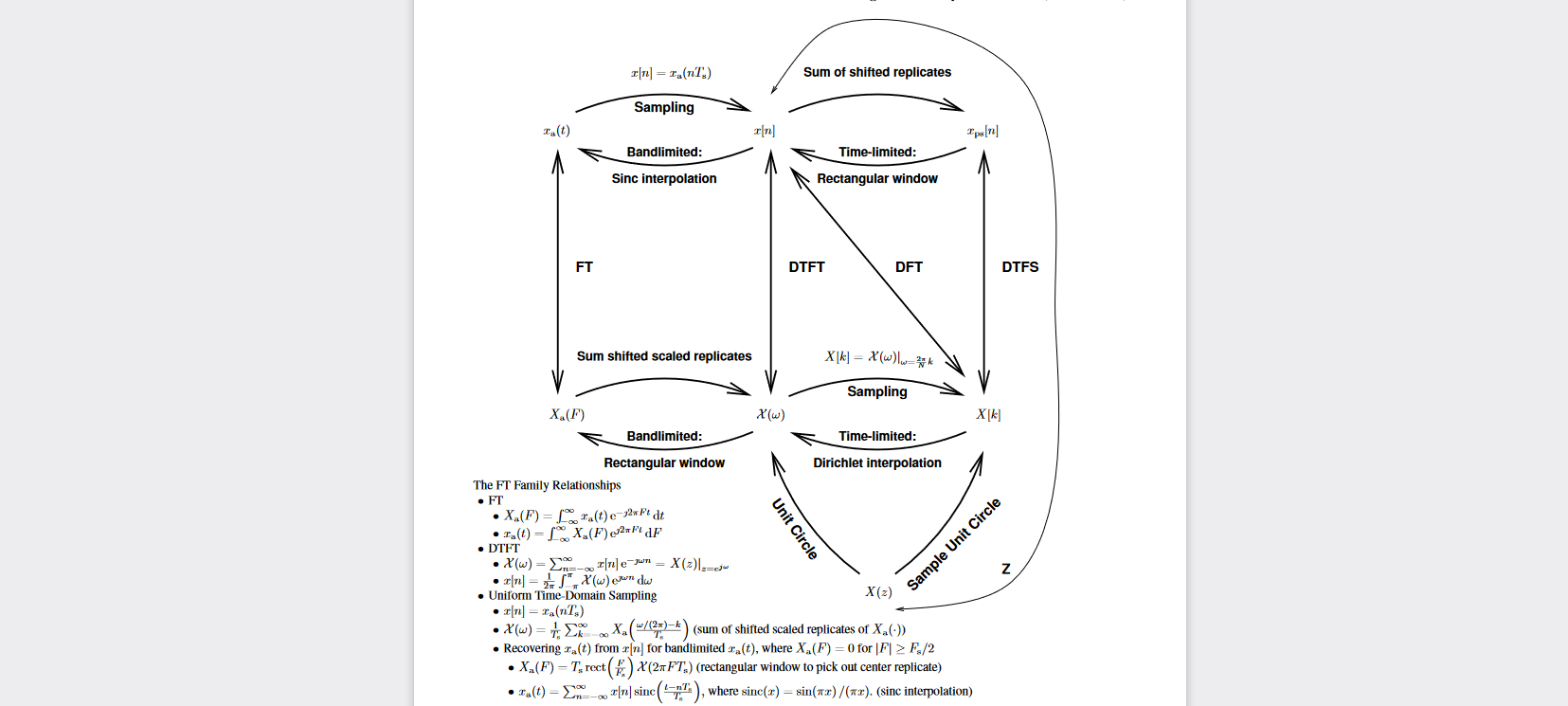

数字信号处理 六、时域数字信号处理之离散时间傅里叶变换

数字信号处理 六、时域数字信号处理之离散时间傅里叶变换 傅里叶论文:任何连续周期信号都可以由一组适当的正弦曲线组合而成 拉普拉斯赞成,拉格朗日反对 理论上,拉格朗日是对的;应用上,傅里叶是对的 为什么用正弦信号 正弦信号是周期的,分析容易。 正弦曲线的保真度,经过LTI后仍然是正余弦曲线 正余弦互为导数 基本思想 用对已知函数加权求和的方法表示出一个未知的函数。其中的权(系数),就是原函数影射至相应函数组的结果 对于需要研究的y[n],定义y[n]=Σiwixi[n]y[n]=\Sigma_{i}w_ix_i[n]y[n]=Σiwixi[n] 或者 y(t)=∫kwkxk(t)y(t)=∫_kw_kx_k(t)y(t)=∫kwkxk(t) 进而研究wi,其中wi是y[n]在xi[n]上的性质 此方法的好处 y[n]中每个点都是独立的 x[n]可用多种“工具盒” 傅里叶变换 傅里叶变换是最经典常见基础的变换方法 研究wi 研究xi[n] 研究y[n] 期末考点 分类:傅里叶变换(非周期连续信号)、傅里叶级数(周期性连续信号)、离散时域傅里叶变换(非周期离散 ...

汇编语言与逆向技术基础 七、区块表、输入表、输出表

汇编语言与逆向技术基础 七、区块表、输入表、输出表 本章知识点 区块表 输入表 输出表 区块表 保证程序的安全性 把 code 和 data 放在同一个内存区块中相互纠缠,很容易引发 安全问题 code 有可能被 data 覆盖,导致崩溃 PE 文件格式将内存属性相同的数据统一保存在一个被称为“区块”(Section )的地方 内容 Name 8 BYTE :块名 VirtualSize DWORD:在 内存空间 中,区块的大小 VirtualAddress DWORD:区块在 内存空间 中的起始 RVA SizeOfRawData DWORD:该区块在 硬盘 中所占的空间 PointerToRawData DWORD:该区块在 硬盘 中的偏移 PointerToReLocations DWORD: 在 EXE 文件中无意义 PointerToLinenumbers DWORD: 行号表在文件中的偏移量 NumberOfReLocations WORD: 在 EXE 文件中无意义 NumberOfLinenumbers WORD: 该块在行号表中 ...

网络技术与应用 第六章 IP 数据报

IP 数据报的格式 包含报头区和数据区 报头区:为了正确传输高层数据而增加的控制信息 数据区:高层传输的数据 报头区 版本与协议:4/6 长度:报头有两个表示长度的字段,一个表示报头长度,一个表示总长度 服务类型:低延迟/高吞吐率/可靠性高 生存周期 头部校验和 地址 数据区 包含上层的报头和报文 IP 封装、分片与重组 分片 MTU 最大传输单元 重组 到目的主机才重组 分片控制 标识、标志和片偏移 一个片偏移对应8个字节 标志:是否已分片,是否是最后一片 数据报选项 主要用于控制和测试 用户可以使用也可以不使用 IP 选项,但所有实现 IP 协议的设备必须能处理 IP 选项 IP 数据报选项由选项码、长度和选项数据3部分组成 源路由选项 源路由:IP 数据报穿越互联网经过的路径是由源主机指定的 严格路由和松散路由 记录路由选项 记录 IP 数据报从源主机到目的主机所经过路径上的各个路由器 IP 地址 时间戳 差错与控制报文 IP 互联网利用 ICMP 传输控制报文和差错报文 ICMP 差错报文 基本功能:提供差错报告,不规定采取什么处理方式 ICMP ...

CA8 指令级并行性 (2)

CA8 指令级并行性 (2) Tomasulo 算法 提出 动态确定某条指令何时可以执行 重命名寄存器以避免不必要的危害 基本思路 保留站尽快取入和缓存有效的操作数 待执行指令说明为其提供操作数的功能单元 在重叠执行期间,对同一个寄存器连续写操作,只有最后一个写操作用来实际更新寄存器 特点 跟踪指令的操作数何时可用——最小化RAW危害 寄存器重命名——最小化WAW和WAR危害 亮点 保留站 reservation station:缓存待发出指令的操作数或关联的功能单元——完成寄存器重命名的工作 缓存等待发出指令的操作数,并与功能单元关联 指令不再需要从寄存器中获取操作数 公共数据总线 common data bus:“广播”功能单元的执行结果 总线特点 普通数据总线:数据+目——“去哪儿”总线 公共数据总线:数据+源——“从哪来”总线 Tomasulo算法处理器的基本结构 四个步骤 发出issue/派遣dispatch 从指令队列头部获得下已条指令(FIFO方式保证正确的数据流) 如果保留站RS可用,则向其发出带有操作数数 ...

计算机网络 第四章 网络层协议

Kapitel 4 网络层协议 提纲 网络层功能 IP协议(数据面) IPv4数据包格式和地址 IPv4数据包转发 IPv4地址问题及解决策略 IPv6基础 ICMP协议 路由算法(控制面) 链路状态算法 距离向量算法 互联网路由协议:RIP,OSPF, BGP 软件定义网络(SDN) 4.1 网络层功能 网络层功能部署 网络层在每台主机和路由器中实现 发送端:将传输层数据单元封装在数据包中 接收端:解析接收的数据包中,取出传输层数据单元,交付给传输层 路由器:检查数据包首部,转发数据包 网络层关键功能 路由(控制面):决定数据包从源主机到目的主机的路径 核心:路由算法与路由协议 转发(数据面):将数据包从路由器的输入接口送到输出接口的过程 控制面分为分布式的和集中式的 4.2 IP协议-IP服务 面向无连接的数据报服务 不需要提前建立连接 数据包基于目的主机地址进行转发 数据包独立转发,相同源-目的的数据包可能经过不同的路径 尽力而为(Best-effort)的不可靠服务 数据包可能会产生较长的时延 数据包可能会丢失、失序、重复 ...

汇编语言与逆向技术基础 六、PE 文件结构

汇编语言与逆向技术基础 六、PE 文件结构 本章知识点 可执行文件 PE 文件结构 DOS 文件头 PE 文件头 为什么Windows上的exe文件不能在Linux或MacOS上运行? 答:文件结构不一样 可执行文件 可执行文件 executable file 由操作系统进行加载、执行的文件 在不同的操作系统环境下,可执行文件的格式不一样 二进制文件,不同于txt、doc、excel等文本文件 Windows 系统可执行文件 在 Windows 操作系统下,可执行文件可以是 .exe 文件、.sys 文件、.dll 文件、.com文件等类型文件 .com 文件 主要用于命令行应用程序,最大 65280 字节 与 MS-DOS 操作系统的可执行文件兼容 .exe .dll .sys 可执行文件 使用 PE 文件结构 PE 可移植可执行文件结构 逆向技术的基础 PE 文件结构 PE 文件使用的是一个平面地址空间 所有的代码和数据合并在一起,组成一个很大的结构 文件内容被分割位不同的节(Section) 节 代码节.code、数据 ...